# DATA MOVEMENT LIMITS TO FRONTIER MODEL TRAINING

Ege Erdil<sup>\*</sup> Epoch AI ege@epochai.org David Schneider-Joseph\* david@davidsj.com

# Abstract

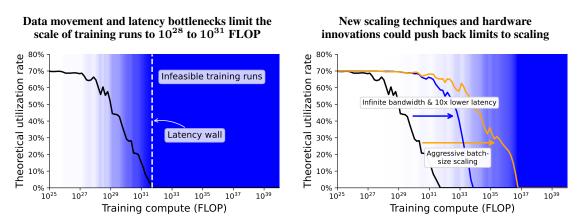

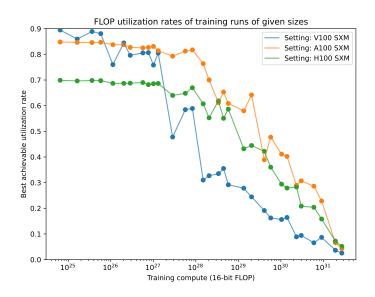

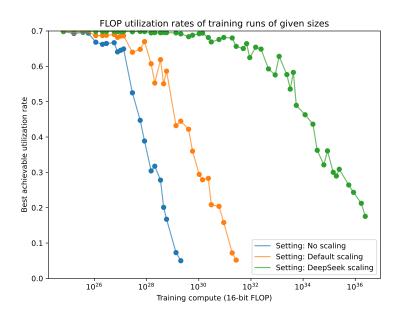

We present a theoretical model of distributed training, and use it to analyze how far dense and sparse training runs can be scaled. Under our baseline assumptions, given a three month training duration, data movement bottlenecks begin to significantly lower hardware utilization for training runs exceeding about  $10^{28}$  FLOP, two orders of magnitude above the largest training run to date, **suggesting the arrival of fundamental barriers to scaling in three years** given recent rates of growth. A training run exceeding about  $10^{31}$  FLOP is infeasible even at low utilization. However, more aggressive batch size scaling and/or shorter and fatter model shapes, if achievable, have the potential to permit much larger training runs. An interactive version of our model will shortly be accessible here.

# **1** INTRODUCTION

Scaling up neural networks and training them on more examples is crucial for good task performance (Hestness et al., 2017; Kaplan et al., 2020; Hoffmann et al., 2022; Bi et al., 2024), with state-of-the-art models requiring tens of thousands of GPUs<sup>1</sup> to train in a reasonable duration. Previous work (Huang et al., 2019; Rajbhandari et al., 2020; Lepikhin et al., 2020; Narayanan et al., 2021; Jiang et al., 2024b) has developed practical techniques enabling the rapid scaling of the past decade (Sevilla et al., 2022).

In this work, we address unexamined fundamental questions about **limits to scaling in the future:**

- **Q1** Given present-day algorithms, GPUs, and interconnects, what is the biggest training run that can be performed within a fixed duration, before intra- and inter-GPU data movement starts to seriously worsen utilization or even render it impossible?

- Q2 How far might this limit be extended, and what algorithmic or hardware progress can achieve that?

Answering these questions empirically would require millions of GPUs and large-scale engineering efforts, so we instead approach them theoretically. In doing so, we develop a simulator that can find optimal training run configurations accounting for the factors that we identify as fundamental. This gives us the answers:

A1 With most current technology, GPU utilization starts to fall at  $\approx 10^{28}$  floating point operations (FLOP), about three years away at recent trends (Epoch AI, 2024) of  $4.2 \times$  growth per year.

<sup>\*</sup>Equal contribution.

<sup>&</sup>lt;sup>1</sup>We focus on GPUs, but our theoretical model and findings are broadly applicable to other accelerators, and even groups of accelerators.

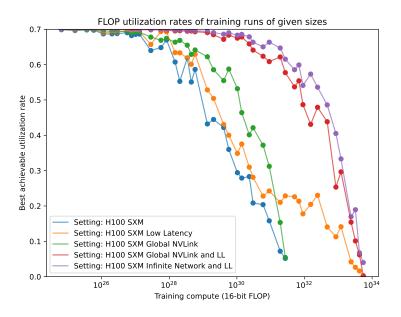

Currently-available specialized high-bandwidth inter-node interconnects can permit training runs about two orders of magnitude larger ( $\approx 10^{30}$  FLOP), at which point latencies begin to worsen utilization, until reaching **an absolute latency barrier at**  $\approx 10^{31}$  FLOP, about seven years away.

A2 Improved hardware interconnects may buy no more than two orders of magnitude in training run size, assuming technology anything like the current paradigm. Beyond that, the critical innovations must come from machine learning algorithms: The key challenge is transforming two serial dependencies — between batches and between layers — into opportunities for parallelism, by making batch sizes bigger (perhaps enabled by sparsity) and models wider and shallower. Achieving these goals may be quite difficult in practice.

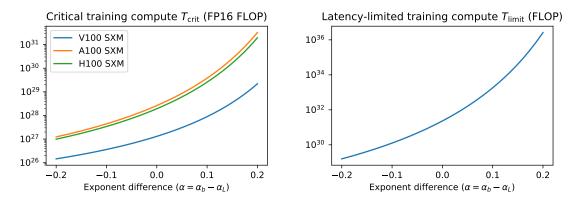

Figure 1: With current technology, such as the H100 GPU and current scaling techniques, data movement bottlenecks lower hardware utilization for training runs exceeding  $10^{28}$  FLOP, and a "latency wall" renders surpassing  $10^{31}$  FLOP infeasible (left). However, with innovations in scaling (such as techniques to enable much larger batch sizes) or dramatic increases in network bandwidth coupled with a  $10 \times$  reduction in interand intra-GPU latency, training runs can be at least a few orders of magnitude larger (right).

This work is organized as follows:

- Section 2 introduces a simplified model of a neural network consisting of stacked sparse linear multi-layer perceptrons that we use as the basis for our analysis throughout the paper.

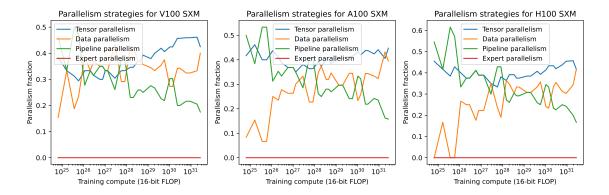

- Section 3 provides an overview of the four main parallelism strategies employed in distributed training—data, tensor, pipeline, and expert parallelism—and summarizes their communication costs.

- Section 4 identifies the key factors that constrain distributed training, including data movement, critical batch size, and latency, and model depth.

- Section 5 derives closed-form expressions for the maximum training scale under this model.

- Section 6 presents the complete theoretical model accounting for all identified constraints and discusses simulation results on current hardware, demonstrating the limits to efficient scaling.

We conclude by discussing the implications of our findings, and posing key open technical questions whose answers will determine the limits to large-scale model training.

# 2 A TOY MODEL: STACKED SPARSE LINEAR MLP BLOCKS

We first carefully define the class of models to be considered. Since the Transformer (Vaswani et al., 2017), including its sparse varieties (Fedus et al., 2022), is the dominant architecture today for frontier models, it seems a natural baseline. As we will show momentarily, the great majority of computation when training a Transformer occurs in its linear layers, so we adopt a simplified model consisting of these elements. This approach has the advantage that such layers also constitute the bulk of computation in many alternative architectures (Peng et al. (2023) and Gu & Dao (2023) among others), so our model retains applicability to a wide variety of potential future algorithmic developments. However, the huge space of possible unexpected algorithmic developments precludes any watertight guarantees, should state-of-the-art architectures or learning algorithms change drastically.

The formal definitions we make are as follows: a sparse linear multi-layer perceptron (MLP) block ("MLP block" for short) consists of learnable weight matrices  $W_1^e \in \mathbb{R}^{d_{\text{ff}} \times d_{\text{model}}}$  and  $W_2^e \in \mathbb{R}^{d_{\text{model}} \times d_{\text{ff}}}$  for expert indices e in the range  $1 \le e \le E$ , where E is the sparsity factor of the model.

Given a matrix of input vectors  $X_{in} \in \mathbb{R}^{d_{model} \times b}$ , where *b* is the batch size in units of tokens, a router  $\rho : \mathbb{R}^{d_{model}} \to \{1, \ldots, E\}$  (assumed to be computationally inexpensive) chooses some expert index  $\rho(X_{in}^k)$  for each token index  $k \leq b$ . The sparse linear MLP *f* then yields an output matrix  $X_{out} = f(X_{in}) \in \mathbb{R}^{d_{model} \times b}$  by mapping each token's input column  $X_{in}^k$  to the corresponding output column  $X_{out}^k$  via the weight matrices corresponding to the chosen expert. If (e) indexes the set of tokens routed to expert *e*, then:

$$X_{\mathrm{out}}^{(e)} = W_2^e \Big( W_1^e X_{\mathrm{in}}^{(e)} \Big). \label{eq:Xout}$$

We optimistically assume *balanced routing* (Section 3.2.2): the same number b/E of tokens is routed to each of the E experts, so that during the forward pass every expert performs matrix multiplications of shapes  $(d_{\rm ff}, d_{\rm model}) \times (d_{\rm model}, b/E) \rightarrow (d_{\rm ff}, b/E)$  and then  $(d_{\rm model}, d_{\rm ff}) \times (d_{\rm ff}, b/E) \rightarrow (d_{\rm model}, b/E)$ , each requiring  $d_{\rm model}d_{\rm ff}b/E$  multiply-accumulate (MAC) operations. Across both linear layers of all E experts, the MLP block's total arithmetic cost is  $2d_{\rm model}d_{\rm ff}b$  MAC. We then assume L MLP blocks in total, so that the model's forward pass is their composition:

$$F(X) = f_L(f_{L-1}\cdots(f_1(X))).$$

Across these L blocks, the model has

$$N_{\rm p} = 2LEd_{\rm model}d_{\rm ff} \tag{1}$$

parameters in total and a forward pass on a batch size of b requires  $N_{\rm p}b/E = 2Ld_{\rm model}d_{\rm ff}b$  MAC.

During the backward pass, gradients of the loss  $\mathcal{L}$  must be computed for the inputs (activations and weights) of each matrix multiplication. A matrix multiplication C = AB of shape  $(I, K) \times (K, J) \rightarrow (I, J)$  on the forward pass becomes two matrix multiplications,

$$\frac{\partial \mathcal{L}}{\partial A} = (\partial \mathcal{L}/\partial C)B^{\top},$$

$$\frac{\partial \mathcal{L}}{\partial B} = A^{\top}(\partial \mathcal{L}/\partial C),$$

of shapes  $(I, J) \times (J, K) \to (I, K)$  and  $(K, I) \times (I, J) \to (K, J)$  on the backward pass, all requiring the same number IJK of MAC. Thus accounting for the backward pass, the number of MAC for our model F is tripled and becomes  $6Ld_{model}d_{ff}b$ .

An actual Transformer has linear layers not only in its MLP but also for attention queries, keys, values, and outputs. These can be fused with and computed in parallel with the MLP block (Wang & Komatsuzaki, 2021; Chowdhery et al., 2022), so that our simplified model encompasses these. However, there are also operations which we neglect:

- Element-wise operations such as nonlinear activation functions,<sup>2</sup> layer normalization (Ba et al., 2016), and residual accumulation (He et al., 2015). We treat these as negligible as they involve  $O(d_{\text{model}})$  or  $O(d_{\text{ff}})$  computations per token, as compared to the linear layers'  $O(d_{\text{model}}d_{\text{ff}})$  computations per token. For large language models,  $d_{\text{model}}$  is typically on the order of  $10^4$ , and  $d_{\text{ff}}$  a multiple thereof, so relative negligibility tends to hold in practice. Furthermore, these element-wise operations need not impose additional significant data movement of their own, as they can often be fused with matrix multiplication kernels.

- Embedding and unembedding projections  $W_{\text{embed}} \in \mathbb{R}^{d_{\text{model}} \times V}$ ,  $W_{\text{unembed}} \in \mathbb{R}^{V \times d_{\text{model}}}$ . As these are computed only once per forward pass rather than once per Transformer block, and the vocabulary size V is typically not much larger than  $d_{\text{ff}}$ , we ignore these.

- Scaled dot-product attention scoring and the corresponding linear combination of the attention head value vectors. For a sequence length  $\ell$  and typical attention width  $n_{\text{heads}} \cdot d_{\text{head}} \approx d_{\text{model}}$ , this requires  $O(\ell d_{\text{model}}b)$  MAC per attention layer each batch. While not completely negligible, this cost is typically small compared to the MLP MAC  $\approx 2d_{\text{model}}d_{\text{ff}}b$  above, as the sequence length  $\ell$  is usually significantly smaller than the internal MLP width  $d_{\text{ff}}$  during most of training. (Dubey et al., 2024; Devlin et al., 2019)

We thus see that our toy model, despite being dramatically simpler to analyze and understand than an actual Transformer, encompasses most of its arithmetic work.

We have so far considered only arithmetic costs. To understand bottlenecks to distributed training, we must also investigate the costs of data movement, both within and between GPUs. Much of what follows will concern itself with this investigation.<sup>3</sup> To proceed, we must first understand how the work of a training run can be distributed across GPUs.

# 3 METHODS OF PARALLELISM

The workload of a training run can be distributed through a variety of methods (Weng & Brockman, 2022): data parallelism (DP), tensor parallelism (TP), pipeline parallelism (PP), and expert parallelism (EP), corre-

<sup>&</sup>lt;sup>2</sup>Logically, dropping the nonlinearities makes a dense Transformer architecture trivial, as the end-to-end map F becomes linear and thus representable by a single matrix. We assume the nonlinearities are still present, but omit modeling them due to their relative computational insignificance.

<sup>&</sup>lt;sup>3</sup>Beyond our toy model, element-wise operations need not impose additional significant data movement of their own, as they can often be fused with matrix multiplication kernels. Even when not, the volume tends to be small relative to weight matrices due to slicing along the batch dimension from data and pipeline parallelism into very small nanobatches (Section 5.1), necessitating many accesses of the same weight matrix per batch. Scaled dot-product attention can impose additional data movement, especially if the nanobatch size is significantly smaller than the sequence length, which will be one of several factors causing our results to err on the optimistic side. Actual achieved training run sizes and utilizations will likely be bounded above by our model.

sponding to the four problem dimensions: batch size, layer width, model depth, and sparsity, respectively.<sup>4</sup> This list of parallelism methods is also exhaustive, because a single matrix multiplication only allows for tensor and data parallelism. Further parallelism must come from assigning different matrix multiplications to different GPUs, which can be done vertically (pipeline parallelism) or horizontally (expert parallelism). In this section, we briefly overview these methods, organized by their characteristic communication patterns.

# 3.1 TENSOR SLICING AND ALL-REDUCE: DATA AND TENSOR PARALLELISM

Consider a forward pass matrix multiplication C = AB of shape  $(I, K) \times (K, J) \rightarrow (I, J)$  and its backward pass computations  $\partial \mathcal{L}/\partial A = (\partial \mathcal{L}/\partial C)B^{\top}$  and  $\partial \mathcal{L}/\partial B = A^{\top}(\partial \mathcal{L}/\partial C)$  as described in Section 2. For example, A could be the weight matrix  $W_1^e$  for an expert's first layer, and B its input activations  $X_{in}^{(e)}$ , in which case the forward pass multiplication shape is  $(d_{\rm ff}, d_{\rm model}) \times (d_{\rm model}, b/E)$ , as discussed earlier.

#### 3.1.1 ONE-DIMENSIONAL SLICING

A natural idea is to partition the data (and associated work) along one of the dimensions of size I, J, or K, while replicating the other dimensions. When this is the expert's batch dimension of size b/E, we call this **data parallelism**, and when it's one of the layer shape dimensions  $d_{\text{model}}$  or  $d_{\text{ff}}$ , we call it **tensor parallelism**. Fundamentally they require the same communication pattern, which we now describe in general terms.

If the data is partitioned along the "internal" K-sized dimension into K'-sized chunks across  $N_K = K/K'$  GPUs, and the computation partitioned accordingly, then the  $n^{\text{th}}$  GPU performs a matrix multiplication of shape  $(I, K') \times (K', J) \rightarrow (I, J)$ , defined by:

$$c_{ij}^{(n+1)K'-1} = \sum_{k=nK'}^{(n+1)K'-1} a_{ik}b_{kj}.$$

Each GPU thus has only a partially-reduced value for each component of C, but requires the fully-reduced component  $c_{ij} = c_{ij}^0 + c_{ij}^1 + \ldots + c_{ij}^{N_K-1}$  so that it may proceed with the next computation step. This necessitates an **all-reduce** collective communication across the  $N_K$  GPUs. (Kumar et al., 1994)

We can derive the minimal inter-GPU data movement volume for this all-reduce, assuming that messages contain the single-word partial sum accumulated so far by the transmitting GPU. Given any total ordering of messages consistent with their causal partial ordering, the  $(N_K - 1)$ <sup>th</sup> message is the first whose receiver can possibly lie causally downstream of all other GPUs and therefore contain the fully-reduced component  $c_{ij}$ . The other  $N_K - 1$  GPUs must then also receive at least one additional message, so there must be at least  $2(N_K - 1)$  messages, and hence words, received in total.<sup>5</sup>

That is, to all-reduce a single word across  $N_K$  GPUs, each GPU must receive

$$2(N_K - 1)/N_K \approx 2 \tag{2}$$

words.

<sup>&</sup>lt;sup>4</sup>For a Transformer, *sequence parallelism* is also available, partitioning work even across different tokens in the same sequence. This can be thought of as data parallelism with some additional communication for the attention layers. We omit discussion of this method because of our restricted focus on linear layers.

<sup>&</sup>lt;sup>5</sup>Strictly speaking, not every word need be received by a *GPU* per se, but merely by some network device. For example, the network fabric can cut GPU all-reduce bandwidth requirements by about  $2\times$ . (Graham et al., 2016)

There are  $I \cdot J$  such components, so this matrix multiplication's all-reduce must cost at least

$$2IJ(N_K-1)$$

words of inter-GPU data movement.<sup>6</sup> This lower bound can in fact be achieved exactly by, for example, consecutively performing a reduce-scatter and an all-gather operation (Kumar et al., 1994).

On the backward pass matrix multiplications of shapes  $(I, J) \times (J, K) \rightarrow (I, K)$  and  $(K, I) \times (I, J) \rightarrow (K, J)$ , the K-sized dimension is "external", hence requires no reduction, and therefore no inter-GPU communication.

If instead the data is partitioned across  $N_I$  GPUs along the *I*-sized dimension, then this dimension is "internal" (i.e. requiring reduction) only for the second backward pass matrix multiplication of shape  $(K, I) \times (I, J) \rightarrow (K, J)$ , imposing

$$2KJ(N_I-1)$$

words of inter-GPU data movement in the backward pass, and none in the forward pass. Symmetrically, a partition across  $N_J$  GPUs along the *J*-sized dimension requires

$$2IK(N_J-1)$$

words of inter-GPU data movement in the backward pass, and none in the forward pass.

#### 3.1.2 MULTI-DIMENSIONAL SLICING

In general, we may partition the data across  $N = N_I N_J N_K$  GPUs, with each performing a forward pass multiplication of shape  $(I', K') \times (K', J') \rightarrow (I', J')$ , where as before we define  $I' = I/N_I$ , etc.

Because communication in the forward pass happens only along the "inner" K-sized dimension, this can be treated as  $N_I N_J$  independent matrix multiplications, entailing (as derived above)  $2I'J'(N_K - 1)$  words of inter-GPU data movement each. Across all independent multiplications, this works out to  $2(N_I I')(N_J J')(N_K - 1) = 2IJ(N_K - 1)$  words of inter-GPU data movement in the forward pass, exactly as in the K-only parallelism case.

We find similarly for backward pass communication across the I and J dimensions, so that:

total inter-GPU data movement =

$$2[IJ(N_K - 1) + KJ(N_I - 1) + IK(N_J - 1)]$$

words. (3)

Let us now consider intra-GPU data movement between main DRAM memory and the logic chip.<sup>7</sup> Assuming an ideal cache, each forward pass matrix multiplication loads I'K' + K'J' words from memory and writes I'J' words to memory, for

$$I'K' + K'J' + I'J'$$

<sup>&</sup>lt;sup>6</sup>Here and throughout, we count only words received. Words transmitted will always either be equal, or (in a multicast setting) at least proportional.

<sup>&</sup>lt;sup>7</sup>See Appendix 8.1 for a discussion of data movement between SRAM-based caches, shared memory, register banks, and execution units.

words accessed per GPU in the forward pass. The two backward pass multiplications behave similarly, tripling total memory IO, so that across all  $N_I N_J N_K$  GPUs we have<sup>8</sup>

total intra-GPU data movement =

$$3(IJN_K + KJN_I + IKN_J)$$

words.

Note the similarity to the inter-GPU data movement formula Eq. 3 above, both having  $N_I, N_J, N_K$ -dependent term proportional to  $IJN_K + KJN_I + IKN_J = IJK(1/I' + 1/J' + 1/K')$ , or simply

$$1/I' + 1/J' + 1/K', (4)$$

when we hold the problem dimensions I, J, K constant.

If we also hold the total number of GPUs N – and thus the per-GPU problem size I'J'K' = IJK/N – constant, we find Eq. 4 is minimized when I' = J' = K', that is when all three degrees of parallelism are sized so as to give each GPU a cube-shaped work unit. In practice the constraint that  $N_I, N_J, N_K$  be positive integers means this exact condition is rarely achieved, and when N is particularly small, the smallest dimensions go un-parallelized. As our concern is the limits to distributed training, we typically consider regimes where N is quite large and the condition approximately holds.

We now apply this analysis to the concrete cases of data and tensor parallelism.

# 3.1.3 DATA PARALLELISM

In this case, each expert's activations  $X_{in}^{(e)}$  and  $X_{out}^{(e)}$  (as well as intermediate states  $W_1^e X_{in}^{(e)}$ ) are sliced  $N_{\text{DP}}$ -way along the b/E-sized batch dimension. This becomes a reduction dimension in the backward pass when computing gradients with respect to the (replicated) weight matrices  $W_1^e$  and  $W_2^e$  (via multiplications of shapes  $(d_{\text{ff}}, b/E) \times (b/E, d_{\text{model}})$  and  $(d_{\text{model}}, b/E) \times (b/E, d_{\text{ff}})$ ), so data parallelism necessitates an all-reduce of weight gradients across the batch dimension, with inter-GPU data movement per weight matrix of  $2d_{\text{ff}}d_{\text{model}}(N_{\text{DP}} - 1)$  words per batch, as can be seen by applying Eq. 3 to this case.

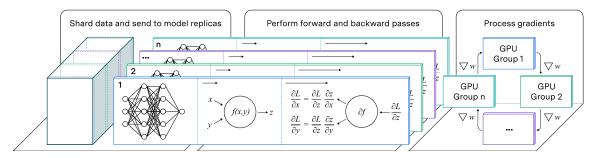

Figure 2: Data parallelism. The input data is divided into shards and processed independently by multiple model replicas. Each replica computes gradients for its local shard, which are then all-reduced across all replicas to obtain the full batch gradient. This full gradient finally updates the model parameters on each replica.

<sup>&</sup>lt;sup>8</sup>In fact, caching is imperfect, increasing required IO, while some opportunities for cache hits across matrix multiplications can decrease this IO. We treat this as a first-order approximation in the regime where the matrices on each GPU are large enough that they would not fit into SRAM – our full model also considers the scenario where the matrices are sufficiently small that we can cut out DRAM reads and writes altogether.

Aggregating across the L MLP blocks, E experts per block, and two layers per expert, this amounts to a total inter-GPU data movement of  $4LEd_{\rm ff}d_{\rm model}(N_{\rm DP}-1)$  words per batch, i.e.

$$2N_{\rm p}(N_{\rm DP}-1)/N_{\rm DP}$$

words per batch per data-parallel worker, where  $N_{\rm p} = 2LEd_{\rm ff}d_{\rm model}$  is the total number of model parameters.

Across those E experts, each data-parallel worker sees  $b/N_{DP}$  tokens. Naively implemented, each stores a full copy of the  $N_p$  model parameters and associated optimizer state. However, the optimizer state can be sharded by inserting the optimizer step *in between* a reduce-scatter/all-gather all-reduce implementation: first the gradients are reduce-scattered, then each worker optimizes the weights corresponding to its gradient partition, then the new weights are all-gathered across workers. (Rajbhandari et al., 2020)

#### 3.1.4 TENSOR PARALLELISM

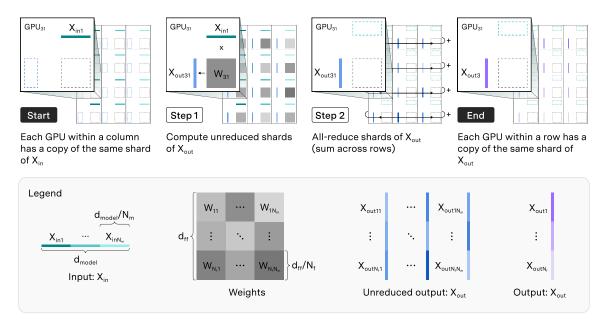

In this case, an expert's activations and weights are sliced into  $N_{\text{TP}} = N_{\text{TP, ff}} \times N_{\text{TP, model}}$  partitions, along the  $d_{\text{ff}}$  and  $d_{\text{model}}$  dimensions. The  $d_{\text{model}}$  dimension is internal in the first layer's forward pass of shape  $(d_{\text{ff}}, d_{\text{model}}) \times (d_{\text{model}}, b/E)$ , as well as the second layer's activation gradient computation of shape  $(d_{\text{ff}}, d_{\text{model}}) \times (d_{\text{model}}, b/E)$ . Symmetrically, the  $d_{\text{ff}}$  dimension is internal in the second layer's forward pass and the first layer's activation gradient computation. Applying Eq. 3, we see  $2(b/E)[d_{\text{ff}}(N_{\text{TP, model}} - 1) + d_{\text{model}}(N_{\text{TP, ff}} - 1)]$  words of inter-GPU data movement for each of an expert's two layers. Aggregating across the L MLP blocks, E experts per block, and two layers per expert, we have total inter-GPU data movement of

$$4Lb[d_{\rm ff}(N_{\rm TP, model}-1)+d_{\rm model}(N_{\rm TP, ff}-1)]/N_{\rm TP}$$

words per batch per tensor-parallel worker.

From our general analysis above, we see that when  $N_{\text{TP}}$  is small (the norm today), the smaller dimension  $d_{\text{model}}$  goes un-partitioned ( $N_{\text{TP, model}} = 1$ ), yielding **1D tensor parallelism**, but that otherwise (as for the much larger training runs which are our focus), **2D tensor parallelism** becomes optimal, with  $d_{\text{ff}}/N_{\text{TP, ff}} \approx d_{\text{model}}/N_{\text{TP, model}}$  (i.e. roughly square weight partitions). Solving this yields approximately

$$8Lb\sqrt{d_{

m model}d_{

m ff}/N_{

m TF}}$$

words of inter-GPU data movement per batch per tensor-parallel worker.

# 3.2 POINT-TO-POINT: PIPELINE AND EXPERT PARALLELISM

We have so far examined partitioning the work along the per-expert batch dimension of size b/E (data parallelism) and the two weight matrix dimensions of size  $d_{model}$  and  $d_{ff}$  (tensor parallelism). Two problem dimensions remain: we can also partition depth-wise across the *L* MLP blocks with **pipeline parallelism**, and/or across the *E* experts with **expert parallelism**. In this case, a given token at a given layer is processed by the GPU (or GPUs, if combined with tensor parallelism) corresponding to that layer's **pipeline stage** and that token's routed expert. As the token moves through the layers during the forward and backward passes, its activations are transferred in a simple point-to-point communication of  $d_{model}$  words whenever crossing pipeline- *or* expert-parallel ranks.<sup>9</sup> Because of the disjunctive nature of this condition, the point-to-point communication cannot always be attributed solely to one or the other method of parallelism, and a joint analysis is warranted.

<sup>&</sup>lt;sup>9</sup>To avoid redundant communication due to replication across tensor-parallel ranks, tensor-parallel all-reduces can be split into two phases: a reduce-scatter *before* the point-to-point communication, followed by an all-gather on the new set of tensor-parallel peers *after* the point-to-point communication. (Narayanan et al., 2021)

Figure 3: 2D tensor parallelism for an MLP block expert's first layer weight matrix W. Start: Input vector  $X_{in}$  is scattered "horizontally" (across  $N_m = N_{\text{TP, model}}$  GPUs) and duplicated "vertically" (across  $N_f = N_{\text{TP, ff}}$  GPUs), and weight matrix shards  $W_{11}$  through  $W_{N_f N_m}$  are scattered along  $d_{\text{ff}}$  (rows) and  $d_{\text{model}}$  (columns) in the same set of GPUs. Step 1: Each GPU computes a partially-reduced shard of output matrix  $X_{\text{out}}$ . Step 2: All-reduce operation across GPU rows computes fully-reduced shards of  $X_{\text{out}}$ . End: Each GPU on a given row has an identical, fully-reduced copy of the  $X_{\text{out}}$  shard corresponding to that row.

Indeed, when the expert-parallel degree  $N_{\rm EP}$  is even moderately large and (as we shall assume) expert routing is stochastically independent of token and layer, then expert-parallel communication *usually* necessitates a point-to-point communication after each MLP block, and so pipeline-parallel communication comes along nearly "for free". However, pipeline parallelism comes with its own challenges, which we now examine.

#### 3.2.1 PIPELINE PARALLELISM

In a naive pipeline-parallel configuration, the first pipeline stage is assigned the first  $L/N_{PP}$  layers, the second is assigned the next  $L/N_{PP}$  layers, *et cetera*. Consequently, in each forward and backward pass, a vector of size  $d_{model}$  has to be communicated a total of  $N_{PP} - 1$  times. The total data movement cost across all GPUs is simply  $d_{model}(N_{PP} - 1)$  activations per forward or backward pass per token.

Because model layers are inherently serial, pipeline parallelism imposes a unique challenge not encountered by the other forms – data, tensor, and expert – of parallelism: minimizing the so-called **pipeline bubble**, the time GPUs spend idle waiting for activations from other pipeline stages. If the entire batch were sent through the pipeline all together, then at any given moment only one of the  $N_{PP}$  pipeline stages would ever be active, and the **bubble fraction** (proportion of time spent idle) would equal  $1 - 1/N_{PP}$ . So instead, the batch must be sliced further than whatever is imposed by data parallelism alone, into smaller pieces called **microbatches**, which travel individually through the pipeline according to a **pipeline schedule** in which, ideally, the large majority of pipeline stages are active most of the time. Narayanan et al. (2021) notes that a naive pipelining strategy (Fig. 4) with m microbatches and  $N_{PP}$ -way pipeline parallelism incurs a bubble

| Device groups   |                    |                |                | Forward pass   |                | Ba             | Backward pass    |                | Bubble         | e (            | Optimizer step      |                |                |                |                |  |

|-----------------|--------------------|----------------|----------------|----------------|----------------|----------------|------------------|----------------|----------------|----------------|---------------------|----------------|----------------|----------------|----------------|--|

| 1               | Residual block 1   | _              | _              | _              | _              |                |                  |                |                |                |                     | <b>_</b>       |                |                |                |  |

|                 | Residual block 2   | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> | F <sub>4</sub> |                |                  |                |                |                |                     | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub> |  |

| 0               | Residual block 3   |                | _              | F <sub>2</sub> | F <sub>3</sub> | _              |                  |                |                |                | /                   | /              |                | / /            |                |  |

| 2               | Residual block 4   |                | F <sub>1</sub> |                |                | F <sub>4</sub> |                  |                |                |                | B <sub>1</sub>      | B <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub> |                |  |

|                 | i                  |                |                | F <sub>1</sub> | F <sub>2</sub> | F3             | F4               |                |                | В1             | ,<br>В <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub> | /              |                |  |

| N <sub>PP</sub> | Residual block L-1 |                |                |                | _              | _              | -                | -              | · · ·          | × –            | · ·                 | × –            |                |                |                |  |

|                 | Residual block L   |                |                |                | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> F | F <sub>4</sub> | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub>      | B <sub>4</sub> |                |                |                |  |

|                 | Time               |                |                |                |                |                |                  |                |                |                |                     |                |                |                |                |  |

Figure 4: Pipeline parallelism. This diagram depicts the sequential execution flow of microbatches  $F_1$  to  $F_4$  during the training of a deep learning model using a GPipe pipeline schedule (Huang et al., 2019). Device groups, each containing one or more GPUs, are allocated distinct sets of model layers, shown here as residual blocks, and they process the microbatches in a staggered fashion. Pipeline bubbles, the white areas, indicate periods of GPU inactivity due to dependency waits. The optimizer step, highlighted in gray, follows the backward passes and is where model parameter updates occur.

fraction of

$$B_{\rm pp} = \frac{N_{\rm PP} - 1}{N_{\rm PP} - 1 + m},\tag{5}$$

or a maximum arithmetic utilization of

$$U_{\rm pp} = 1 - B_{\rm pp} = \frac{m}{N_{\rm PP} - 1 + m}.$$

This can be seen most easily from the perspective of the last stage: on the forward pass it spends  $N_{PP} - 1$  bubble steps waiting for that same number of previous stages, then has m steps of work to perform; the backward pass looks the same in reverse. Since all stages have the same amount of work to do, they must also have this same bubble fraction.

Therefore, it's crucial to ensure that the number of microbatches m is large relative to  $N_{PP} - 1$ , the number of inter-stage interfaces in the pipeline. But this lowers the arithmetic intensity of the computations done by the GPUs by slicing the data matrix further along the per-expert batch dimension b/E, increasing data movement costs *internal to the GPUs*, as the weights and their accumulated gradients must be accessed *once for each microbatch*. Increasing the batch size b is a natural answer to this conundrum, but this too has limits, which we discuss in Section 4.2.

**Pipeline interleaving.** Another solution described by Narayanan et al. (2021) is *pipeline interleaving*. By assigning non-adjacent layers of our model to the same pipeline stage, each microbatch travels through the pipeline *multiple times*, for a different set of model layers each time. This increases the effective microbatch count, shortens the initial (and terminal) serial wait time for work to reach (and clear) all stages, and thereby reduces the bubble fraction  $B_{pp}$ . This comes at the expense of increased network communication, but this trade-off is usually quite favorable, as the point-to-point communication volume imposed by pipeline parallelism (and shared with expert parallelism) is not large.

We leave a detailed discussion of pipeline interleaving to Appendix 8.2. Here, we note only that if the number of microbatches m is at least equal to the number of pipeline stages  $N_{\text{PP}}$ , we can pick any divisor i of  $L/N_{\text{PP}}$  and change the pipeline schedule to achieve the following two outcomes:

- 1. The bubble fraction becomes  $B_{\text{interleaved PP}}(i) = (N_{\text{PP}} 1)/((N_{\text{PP}} 1) + im)$ : the effective number of microbatches determining the bubble fraction goes up by a factor of *i*.

- 2. The total communication cost per forward pass becomes  $d_{\text{model}}(N_{\text{PP}} \cdot i 1)$ : the effective number of pipeline stages determining network communication costs goes up by this same factor *i*.

**Zero bubble pipeline parallelism.** Qi et al. (2024) recently observed that only *activation* gradients are serial dependencies in the backward pass for previous pipeline stages, and hence the computation of *weight* gradients can be deferred to otherwise idle time in order that those earlier pipeline stages may sooner have work. In this way, their ZB-H2 schedule completely eliminates bubbles. Though this schedule has approximately twice the memory footprint of the interleaved schedule from the previous section, this is a negligible cost in large clusters in which device memory is abundant.

The ZB-H2 schedule requires at least  $2N_{PP} - 1$  microbatches to achieve the zero bubble condition, but this is small compared to the much larger number of microbatches required even to approximate this in a traditional schedule.

### 3.2.2 EXPERT PARALLELISM

Expert parallelism involves slicing each layer along the expert dimension E: each pair of weight matrices  $W_1^j$  and  $W_2^j$  for  $1 \le j \le E$  is stored on one of  $N_{\text{EP}}$  expert-parallel ranks, with activation vectors routed to the appropriate rank for their routed expert. Even without any expert parallelism, the sparsity factor E itself already harms the arithmetic intensity of matrix multiplications by shrinking the per-multiplication batch size, and expert parallelism does not in general make matters worse. However, scaling this sparsity factor could potentially increase the largest batch size which can efficiently be used in training (Section 4.2).

In our toy model (Section 2), we consider only settings where each activation vector is routed to a single expert, in which case the point-to-point communication pattern is low-bandwidth and can coincide with that already needed for pipeline parallelism. If tokens are instead routed to multiple experts (Shazeer et al., 2017; Patel & Wong, 2023), with a linear combination taken of their outputs, then a tensor-parallel-style all-reduce across experts is required, potentially across unpredictable levels of the network hierarchy depending on expert placement. As our objective in this paper is to shed light on the limits to distributed training, we make optimistic assumptions when possible. In line with this, we treat the "fine-grained" case as an extension of tensor parallelism and do not model it separately, simplifying our analysis greatly.

Continuing in this spirit, we assume *balanced routing* between experts, independent of token or layer, to ensure uniform workloads across workers. (Lepikhin et al., 2020; Lewis et al., 2021; Zhou et al., 2022)

### 3.3 5D PARALLELISM

*5D parallelism* involves combining all of the parallelism methods we've discussed so far: data, tensor (both dimensions), pipeline, and expert parallelism. Table 1 summarizes the network communication costs of these methods on an equal footing: how much communication they require per gradient step taken.

To see why combining multiple parallelism methods is more efficient than using any one method of parallelism by itself, consider the isolated problem of minimizing the total network bandwidth cost for a cluster given a fixed cluster size  $N_{\text{GPU}} = N_{\text{TP}}N_{\text{PP}}N_{\text{DP}}$  for a dense training run (so that  $E, N_{\text{EP}} = 1$ ). The total bandwidth cost for i = 1 can be expressed as

$$\approx 2N_{\rm p}(N_{\rm DP}-1) + 2bd_{\rm model}(N_{\rm PP}-1) + 8bL\sqrt{d_{\rm ff}d_{\rm model}N_{\rm TP}} = c_{\rm DP}N_{\rm DP} + c_{\rm PP}N_{\rm PP} + c_{\rm TP}\sqrt{N_{\rm TP}} - d,$$

|                      | Network bandwidth per gradient step                                             | Slices along              | Communications can coincide with |

|----------------------|---------------------------------------------------------------------------------|---------------------------|----------------------------------|

| Data parallelism     | $2N_{\rm p}(N_{\rm DP}-1)$                                                      | b                         | Nothing                          |

| Tensor parallelism   | $\approx 8bL\sqrt{d_{\rm ff}d_{\rm model}N_{\rm TP}}$ (for large $N_{\rm TP}$ ) | $d_{ m model}, d_{ m ff}$ | Nothing                          |

| Pipeline parallelism | $2bd_{\text{model}}(N_{\text{PP}}\cdot i-1)$                                    | b, L                      | Expert parallelism               |

| Expert parallelism   | $2bd_{\text{model}}(L-1) \cdot (N_{\text{EP}}-1)/N_{\text{EP}}$                 | E                         | Pipeline parallelism             |

Table 1: The different parallelism methods available along with their network bandwidth costs. Here,  $N_p$  is the number of parameters, b the batch size (in tokens), L the number of MLP blocks,  $d_{model}$  and  $d_{ff}$  the model widths, and i the pipeline interleaving factor.

where  $c_{\text{DP}}, c_{\text{PP}}, c_{\text{TP}}, d$  are strictly positive constants depending on the model dimensions and batch size. In this problem, for  $N_{\text{GPU}}$  sufficiently large<sup>10</sup>, it is optimal to scale all parallelism methods at the same time with the total cluster size  $N_{\text{GPU}}$ , specifically as

$$N_{\rm DP}, N_{\rm PP} \propto N_{\rm GPU}^{1/4}, N_{\rm TP} \propto N_{\rm GPU}^{1/2}$$

This recalls our conclusion in Section 3.1.2 that slicing along multiple problem dimensions is more efficient than slicing along any single one.

In practice, network bandwidth is not the only constraint on distributed training: arithmetic intensity (i.e. memory bandwidth), communication latency, whether that communication can be overlapped with computation, bubble size management for pipeline parallelism, *et cetera* are all relevant factors. These factors can alter the exact quantitative conclusions of the above argument, but the basic intuition that scaling all parallelism methods together is superior to scaling one in isolation generally remains true.

Table 1 also offers insight into some factors that limit the methods from scaling arbitrarily far. Each needs to slice either on one of the two model width dimensions  $d_{model}$ ,  $d_{ff}$  or the batch dimension b. A guideline is that if the amount of computation needed to train a model scales faster than  $d_{ff}d_{model}b$  (the inherently *parallel* problem volume, in contrast to the inherently *serial* dimensions of layer count and optimizer steps) as a model is scaled up, distributed training can hit a bottleneck. We make this guideline quantitative in Section 5.

# 4 WHAT CONSTRAINS DISTRIBUTED TRAINING?

Having discussed the available parallelism methods, we now turn to the main subject of our paper: the obstacles we face if we try to scale some combination of these methods arbitrarily far. Because all these methods incur data movement costs, the arithmetic utilization of the GPUs can fall if a training run becomes bottlenecked by this data movement. We reiterate our key questions:

<sup>&</sup>lt;sup>10</sup>When  $N_{\text{GPU}}$  is small, the constraint  $N_{\text{TP}}$ ,  $N_{\text{DP}}$ ,  $N_{\text{PP}} \ge 1$  will bind on the more expensive parallelism methods, so e.g. the optimal solution is likely to have  $N_{\text{TP}} = 1$  over a wide range of  $N_{\text{GPU}}$  values. This is a big reason why this argument is too simplistic, but it still illustrates the general principle at work.

- **Q1** Given present-day algorithms, GPUs, and interconnects, what is the biggest training run that can be performed within a fixed duration, before intra- and inter-GPU data movement starts to seriously worsen utilization or even render it impossible?

- Q2 How far might this limit be extended, and what algorithmic or hardware progress can achieve that?

In this section, we give a separate account of each fundamental constraint that we identify and model.

#### 4.1 DATA MOVEMENT

Distributed training can run up against data movement limits for two reasons: because we're moving too much data *inside an individual GPU* or *between different GPUs*. We consider each in turn.

#### 4.1.1 INTRA-GPU DATA MOVEMENT

A typical GPU with tensor cores can compute much faster than it can move data to and from DRAM: for example, an NVIDIA H100 SXM (NVIDIA, 2022) can perform a theoretical maximum of  $2 \times 10^{15}$  FLOP/s  $(1 \times 10^{15} \text{ multiply-accumulates (MAC)/s})$  at 8-bit precision during dense matrix multiplications, but has a DRAM memory bandwidth of only 3.35 TB/s, for an **arithmetic intensity** (the ratio of the two) of  $\approx 299$  MAC/byte. An 8-bit matrix multiplication of shape  $(M, K) \times (K, N) \rightarrow (M \times N)$  must perform MKN MAC and, under ideal caching, read the two input matrices and write the output matrix once each, for MK + KN + MN bytes accessed total. For the H100's computational resources to be balanced, we thus must have  $1/299 \approx (MK + KN + MN)/MNK = 1/M + 1/N + 1/K$ . In the square case,

$$M = N = K \approx 896.$$

If the dimensions are substantially smaller, then the tensor cores must go underutilized as they will be bottlenecked on data movement to and from DRAM. Similar considerations apply at lower levels of the memory hierarchy as well. We discuss this further in Section 5.1 and Appendix 8.1.1.

Distributed training across more GPUs or experts requires splitting the problem and hence reducing at least one of M, N, K, worsening arithmetic intensity.

The main way to counter the degradation in arithmetic intensity is by increasing the dimensions of the matrix multiplications: at least one of  $d_{\text{model}}$ ,  $d_{\text{ff}}$ , b (Section 2), either making the model fatter and shorter, or increasing the batch size. Scaling b runs into the critical batch size limit, and it's not clear how far scaling model width  $d_{\text{model}}$  and  $d_{\text{ff}}$  at the expense of model depth L can go while remaining near the compute-optimal frontier. We discuss these matters in greater detail in Sections 4.2 and 4.4. The broad conclusion is there may be no free lunch for arithmetic intensity.

#### 4.1.2 INTER-GPU DATA MOVEMENT

In addition to data movement inside individual GPUs, distributed training requires the movement of data between them. We quantified this cost in Section 3.

Each GPU has an upper bound to the rate of information it can receive or transmit per unit time. This means that asymptotically, the scaling of the total network bandwidth of a cluster can at most be linear in cluster size, even if the interconnect switches, wires, *et cetera* are costless. In practice, scaling is often *sublinear*. For instance, a high-bandwidth NVLink region may be limited to a single node: GPT-4 (OpenAI (2023)) used clusters of A100s (Patel & Wong, 2023) with an NVLink node size of 8. Increasing the tensor-parallel degree  $N_{\text{TP}}$  for such a cluster thus demands some fraction of bandwidth-hungry all-reduce communication over slower interconnects such as InfiniBand.

Even in an optimistic linear scaling regime where we do not have to rely in part on slower connections at other levels of the network hierarchy, scaling a cluster increases *both* the arithmetic throughput *and* the available network bandwidth proportionally, but the data movement *per GPU* increases as we scale the degrees of parallelism, as seen in Section 3. Thus if we hold the model and batch size constant and simply scale up the training cluster, arithmetic intensity with regard to the network must eventually shrink to the point that this communication becomes a bottleneck.

Even if we scale these dimensions, the question remains whether they scale fast enough relative to total training compute of the model, as  $N_{\text{GPU}}$  must be at least proportional to the training run compute given constant utilization and training duration. The answer depends on factors discussed in Sections 4.2 and 4.4.

## 4.2 The critical batch size

Because data and pipeline parallelism both involve slicing the data matrix along the batch dimension, increasing the batch size b helps with scaling up these two methods of parallelism without damaging arithmetic intensity. This is always doable, but only useful to the extent it reduces noise in the gradient estimate; at some scale, the estimate is precise enough that further noise reductions are not useful. (Shallue et al., 2019)

In an ideal scaling regime, n gradient steps with a batch size b and learning rate  $\eta$  should reduce loss equivalently to taking a single gradient step with a batch size  $n \cdot b$  and learning rate  $n \cdot \eta$  (McCandlish et al., 2018), so increasing the batch size effectively parallelizes the otherwise serial gradient descent steps. However, at some point, called the *critical batch size*, this favorable scaling rapidly hits diminishing returns.

McCandlish et al. (2018) conjecture, based on a second-order approximation, that a gradient step at batch size *b* should ideally reduce loss by

$$\Delta L = \frac{\Delta L_{\max}}{1 + b_{\text{noise}}/b},$$

where  $\Delta L_{\text{max}}$  is the infinite batch size limit, and  $b_{\text{noise}}$  is a "noise scale" at which the dependence of  $\Delta L$  on b goes from linear to sub-linear. In this model, the critical batch size  $b_{\text{crit}}$  is equal to the noise scale  $b_{\text{noise}}$ .

They also conduct experiments and observe that models with smaller loss tend to have larger  $b_{\text{noise}}$  values, but holding loss constant, there is no impact of model size on  $b_{\text{noise}}$ . As model loss decreases throughout training, this also means that  $b_{\text{noise}}$  increases throughout training, allowing larger batch sizes to be used later on in a training run compared to what is efficient at initialization.

The intuition for this is straightforward when we're using cross-entropy loss with respect to a ground truth distribution: a model with a smaller Kullback-Leibler divergence with the ground truth distribution can only be distinguished from ground truth by drawing more samples. Knowing which direction to go in for a useful gradient step certainly requires detecting that the model is not already optimal, so models with a smaller reducible loss per token can accommodate larger batch sizes (in units of tokens). This information-theoretic argument also makes the quantitative prediction that the noise scale  $b_{noise}$  should vary inversely proportionally with the reducible loss of the model, i.e. the Kullback-Leibler divergence of the model with the ground truth distribution.

If this conjecture is correct, and the dependence of the critical batch size on a dense model's properties factors through its reducible loss, then we can leverage the Chinchilla scaling law from Hoffmann et al. (2022) to predict how the critical batch size should scale with the training compute of a dense model. As the reducible loss of a Chinchilla-optimal dense model falls off like  $\propto 1/T^{\alpha}$  where T is the model's training compute and  $\alpha \approx 1/6$ , we would predict that the critical batch size should scale approximately with  $T^{1/6}$ .

On the other hand, Bi et al. (2024) claim to find the scaling relationship  $b_{\rm crit} \propto T^{0.33}$ , although many of their models are overtrained relative to the Chinchilla law. For a fixed total training compute and batch size, an overtrained model must be *smaller* (posing less opportunity for tensor parallelism at high arithmetic intensity) and *train on more tokens*, hence use more serial steps, exacerbating latency bottlenecks (Section 4.3). If batch sizes can be scaled this aggressively even at the Chinchilla-optimal frontier, then opportunities for parallelism abound. Our baseline results employ the more conservative scaling assumption of  $b_{\rm crit} \propto T^{1/6}$ , though we analyze robustness to this assumption in Appendix 8.3.

The above discussion relies on theoretical and empirical analysis of first-order optimization methods. While second-order methods have been investigated for years (Dauphin et al., 2014; Martens & Grosse, 2015; Yao et al., 2020; Liu et al., 2023), they pose significant scalability challenges: Full curvature information is normally intractable to calculate, so approximate and/or infrequent estimates must be used instead. Furthermore, the curvature (and its empirical estimate) can be very small or even negative and vary across the loss landscape, so that damping or trust-region approaches are required for stable learning. For these reasons, it remains unclear if second-order methods will ever be practical for frontier training runs. If they are, it's conceivable that critical batch sizes could greatly increase.

### 4.3 LATENCY

The training of a neural network involves some irreducible number of inherently serial operations, across model layers (2L matrix multiplications in each direction in our toy model) and optimizer steps (with parallelism limits due to the critical batch size, as explained in Section 4.2).

If lower bounds exist on the latency of communication between GPUs and matrix multiplication inside a GPU, then the sequential bottleneck in neural network training sets a lower bound for the duration of the entire training run, per Amdahl's law. In practice, bandwidth limits often become binding before latency limits, but latency limits are nevertheless significant because they are more difficult to overcome.

For example, one can always increase the total amount of bandwidth in a cluster by obtaining more GPUs and more network interconnects: in the bandwidth-bound regime this will reduce the arithmetic utilization of the entire cluster, but overall throughput will still increase. A typical result here might be a decay of  $\propto 1/N_{\rm GPU}^{1/3}$  or  $\propto 1/N_{\rm GPU}^{1/4}$  in the overall utilization rate, in a 3D- or 4D-parallel regime respectively (Section 3). In contrast, if the training process is latency-bound, further cluster scaling will not yield any additional benefits at all and the utilization rate will decay as  $\propto 1/N_{\rm GPU}$ .

The two important sources of latency relevant during distributed training are:

- 1. Network latency: Interconnects used in high-performance computing are optimized to have low latency, but even low-latency interconnects such as InfiniBand still require on the order of 1  $\mu$ s for a single point-to-point communication. Within a single node, the interconnect of choice for NVIDIA GPUs is NVLink, and a typical latency of an all-reduce operation that uses NVLink within a single node of 8 GPUs is on the order  $\approx 10 \ \mu$ s (Jeauguey (2018)).

- 2. Intra-GPU latency: Even when working with a single GPU, there are sources of latency that constrain how quickly matrix multiplications may be performed on a single device. We say more about this in Section 5.2, but to summarize, we empirically measure a floor on matrix multiplication latency on an A100 using cuBLAS at around  $4.5 \ \mu s$ .

These latencies are much too small to matter for current training runs, as a typical duration for one matrix multiplication in a single GPU during the training of a current large language model is on the order of

1 to 10 milliseconds. For instance, Falcon-180B (Almazrouei et al., 2023) used  $d_{\text{model}} = 12288$ ,  $d_{\text{ff}} = 4d_{\text{model}}$ ,  $N_{\text{TP, ff}} = 8$ ,  $b = 2^{22}$  and  $N_{\text{DP}} \cdot N_{\text{PP}} = 512$ . If we assume e.g. 4 times as many microbatches as pipeline stages, their feedforward matrix multiplications on individual GPUs were of the shape  $12288 \times 6144 \times 2048$ . On an A100, such a matrix multiplication takes  $\approx 1$  ms at full utilization.

However, as models become larger they need to be trained on more tokens (Hoffmann et al., 2022) and the critical batch size might not increase proportionally (Section 4.2). In this case, the time taken per gradient step has to fall in order that the entire training run still complete within an acceptable duration, and for very large models it could in principle fall below the timescales at which latency constraints would become binding. In Section 5.2 we conclude that we have  $\approx 4$  OOM more room to scale the training compute of state-of-the-art models before latencies begin to hurt utilization.

#### 4.4 SCALING THE NUMBER OF LAYERS

The need to increase the number of sequential operations in a neural network as the network is scaled up can have adverse effects on how parallelizable the training run of such a model can be, as model layers are inherently serialized. The effect of this is mitigated to some extent by techniques that reduce pipeline bubble sizes (Section 3.2.1) and enable models to be effectively parallelized across the layer dimension. However, when network or GPU latency constraints become binding, avoiding additional serial steps in the forward and backward pass is critical for ensuring good utilization even when these techniques are used.

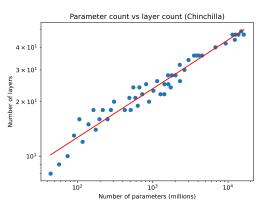

Unfortunately, there is little good research we've been able to find in the literature about what we call *shape* scaling laws: how the performance of a model depends on the balance between its widths (as measured by  $d_{\text{model}}, d_{\text{ff}}$ ) and its depth (as measured by the number of layers L) (Kaplan et al., 2020; Alabdulmohsin et al., 2024). The best we can do is back out implicit laws used in other work, and due to the clean nature of their data and the large number of data points we pick Hoffmann et al. (2022) as our reference in this section. Figure 10 shows the results we obtain by analyzing the information about layer scaling in the models trained in Hoffmann et al. (2022), with the best-fitting scaling law  $L \approx 3.67 \cdot (N_p/10^6)^{0.27}$  where L is the number of layers and  $N_p$  is the number of model parameters.

While this might be nothing more than a rule of thumb, we believe it is nevertheless an important finding because scaling a model by increasing the number of layers generally allows fewer opportunities for parallelism than increasing  $d_{\text{model}}$  or  $d_{\text{ff}}$ . This is because arithmetic intensity constrains the minimum dimensions of the individual matrix multiplications performed by a single device, and without scaling at least one of  $d_{\text{model}}$ ,  $d_{\text{ff}}$ , or *b* the arithmetic intensity cannot effectively be improved. We will see the significance of this in Section 5.1.

### 5 CLOSED-FORM EXPRESSIONS FOR THE BIGGEST TRAINING RUN

In this section and the next, we provide answers to the questions raised in Section 4. We make some simplifications to derive analytic bounds here. After this preliminary analysis, we will introduce a complete model in Section 6 which takes into account all of the constraints that we have previously discussed and closely matches our analytic results.

#### 5.1 THE UTILIZATION CLIFF

Here we derive a closed-form expression upper-bounding the largest achievable training run, before data movement bottlenecks lower utilization substantially.

With even a modest degree of tensor parallelism, its bandwidth consumption greatly exceeds (Table 1) the maximum possible point-to-point communication from pipeline or expert parallelism (e.g. the case  $N_{\text{PP}} \cdot i = L$ ), so we shall neglect their communication cost and take these at their maximum possible degrees

$N_{\text{PP}} = L$ ,  $N_{\text{EP}} = E$ , restricting ourselves to considering only the all-reduce communication from data and tensor parallelism, across  $N_{\text{DP}} \times N_{\text{TP}}$  groups ("workers") of  $N_{\text{PP}} \times N_{\text{EP}} = LE$  GPUs each.

Recalling our discussion of multi-dimensional slicing in Section 3.1.2, and taking  $I = d_{\text{ff}}, K = d_{\text{model}}, J = b/E$  in Eq. 3, the all-reduce communication so imposed is equalized across all three dimensions and minimized when each worker has a cube-shaped unit of work  $(d, d) \times (d, d) \rightarrow (d, d)$  for each matrix multiplication, with some side length

$$d = d_{\rm ff}/N_{\rm TP, \, ff} = d_{\rm model}/N_{\rm TP, \, model} = (b/E)/N_{\rm DP}.$$

(6)

However, given our  $N_{PP} = L$  pipeline stages, we may assume at least  $m \approx 2N_{PP} = 2L$  microbatches, as this is the minimum to achieve the zero bubble condition under a ZB-H2 schedule (Section 3.2.1). This means each actual "physical" matrix multiplication onboard a single GPU corresponding to a single expert and pipeline stage uses a much smaller **nanobatch** size of<sup>11</sup>

$$b' = (b/E)/(N_{\rm DP} \cdot m) = (b/E)/(N_{\rm DP} \cdot 2L),$$

(7)

which is smaller than d by the factor 2L if Eq. 6 holds. Under normal circumstances, this is already a problem for intra-GPU data movement to and from high-bandwidth memory (Section 4.1.1), as this necessitates loading all of an expert's weights, and accumulating their gradients, once for each tiny nanobatch. However, as we are examining the limits to distributed training, we must consider the possibility that each of the  $N_{DP}$ model replicas contains enough individual GPUs such that these weights, along with their gradients, can fit entirely in their aggregate SRAM, perhaps even in register banks. In such a case, their movement is required only once per batch to all-reduce gradients across model replicas, rather than once per nanobatch.

Even so, we cannot normally make the data-parallel degree  $N_{\text{DP}}$  large enough to achieve the ideal of Eq. 6, but instead just large enough that Eq. 7 equals some hardware-specific lower bound b', which we will estimate later using two separate methods. Then our data-parallel degree is

$$N_{\rm DP} = \frac{b}{b'} \cdot \frac{1}{2LE}.$$

(8)

Meanwhile, there is some minimum utilization-preserving weight submatrix size  $d' \times d'$ , which we will also estimate later. This makes our tensor-parallel degree  $N_{\text{TP}} = N_{\text{TP, ff}} \times N_{\text{TP, model}}$  equal to

$$N_{\rm TP} = \frac{d_{\rm ff} d_{\rm model}}{d'^2}.$$

(9)

As discussed above, we assume the maximum possible pipeline- and expert-parallel degrees  $N_{\text{PP}} = L$ ,  $N_{\text{EP}} = E$ , and take  $N_{\text{DP}}$  and  $N_{\text{TP}}$  as in Eqs. 8 and 9 so as to achieve the critical computation volume  $d'^2b'$  per single-GPU matrix multiplication, with a total number of GPUs

$$N_{\text{critical}} = N_{\text{PP}} \cdot N_{\text{EP}} \cdot N_{\text{DP}} \cdot N_{\text{TP}} = \frac{1}{4LE} \cdot \frac{bN_{\text{p}}}{d'^2b'},\tag{10}$$

<sup>&</sup>lt;sup>11</sup>The nanobatch size  $b' = b/(E \cdot N_{\rm DP} \cdot m)$  is the number of tokens seen at once by an individual GPU matrix multiplication kernel, taking into account routing into *E* separate experts (whether or not on separate GPUs), dataparallel sharding of degree  $N_{\rm DP}$ , and sharding into *m* microbatches for pipeline paralellism.

where we have made use of the parameter count formula  $N_{\rm p} = 2LEd_{\rm model}d_{\rm ff}$  (Eq. 1).

Assuming that a cluster of the critical size  $N_{\text{critical}}$  can run at close to full utilization by overlapping data movement with computation, its compute output over a time period  $t_{\text{train}}$  is simply

$$T_{\rm critical} = N_{\rm critical} C t_{\rm train},\tag{11}$$

where C is the arithmetic throughput (MAC/second) of a single GPU at perfect utilization.

Bringing scaling laws into the argument, we now calculate the size of the model that can be trained in a given duration (e.g. 3 months) under the condition that utilization not seriously drop off. Chinchilla scaling laws (Hoffmann et al., 2022) give us a compute-optimal training dataset size of roughly  $20N_p$  tokens, with each training token requiring 3 MAC per parameter, so that the total compute required to train a model with  $N_p$  parameters and sparsity factor E is roughly

$$T_{\text{critical}} = (60 \,\text{MAC}) \cdot N_{\text{p}}^2 / E. \tag{12}$$

Setting Eqs. 11 and 12 equal and substituting in Eq. 10 lets us solve for number of parameters:

$$N_{\rm p} = \frac{b}{L} \cdot \frac{Ct_{\rm train}}{(240\,{\rm MAC})\cdot d'^2b'}.$$

Taking this formula for  $N_{\rm p}$  in Eq. 12,

$$T_{\text{critical}} = \frac{1}{(960 \,\text{MAC}) \cdot E} \left(\frac{b}{L} \cdot \frac{C t_{\text{train}}}{d'^2 b'}\right)^2 \tag{13}$$

is thus an upper bound on the critical training compute at which a model with sparsity factor E, a batch size of b, and a depth of L MLP blocks can be trained over duration  $t_{\text{train}}$  on a cluster of GPUs whose specifications are held fixed, without loss of utilization. This formula is quadratically sensitive to most of its variables, and even quartically sensitive to the critical weight submatrix shape d', so any significant uncertainties can shift our estimate substantially. However, we can use it to place the utilization cliff within an order of magnitude or two.

In practice, we (weakly) expect the batch size b and number of MLP blocks L to scale similarly with training run size: specifically, batch size roughly as  $b \propto T^{1/6} \propto N_p^{1/3}$  (Section 4.2) and layer count roughly as  $L \propto N_p^{0.27}$  (Section 4.4). Since Eq. 13 depends on b and L only through their ratio, an approximation that they are constant may suffice. We will usually assume  $b = 4 \times 10^6$  and L = 100, but explore variations on this assumption in Appendix 8.3, concluding that under more optimistic, but speculative, assumptions, the critical compute threshold  $T_{\text{critical}}$  might increase by about three orders of magnitude.

It is not clear how the sparsity factor E should be scaled. The most recent paper on scaling laws for mixtureof-experts (MoE) models known to us, (Krajewski et al., 2024), is agnostic on the question: the scaling law they derive does not incorporate E as a variable, instead using a fixed value E = 64 following recommendations from Clark et al. (2022). It's also unknown to what degree doing so also permits further compute-efficient scaling of the batch size b. It is apparent from Eq. 13 that if greater sparsity can enable larger batch sizes at a rate exceeding the square root of the sparsity factor, then sparsity permits larger training runs. We'll now pursue two methods to estimate the critical nanobatch size b' and weight submatrix size  $d' \times d'$ , the first from latency bottlenecks, the second from bandwidth bottlenecks.

#### 5.1.1 FROM LATENCIES

Definitionally, b' is the number of tokens in flight at any stage of its processing on a single GPU. So one lower bound for b' and d' comes from the fact that a GPU's unit of work  $d'^2b'$  MAC for each of a nanobatch's matrix multiplications must take at least as long as the irreducible latencies from kernel launches and model- (i.e. tensor-, pipeline-, or expert-) parallel communication. If  $t_L$  is the timescale of this latency, we therefore have:

$$\frac{d'^2b'}{C} \ge \frac{t_L}{\text{MAC}}.$$

Substituting into Eq. 13,

$$T \le \frac{1 \operatorname{MAC}}{960 \cdot E} \left( \frac{b}{L} \cdot \frac{t_{\operatorname{train}}}{t_L} \right)^2.$$

(14)

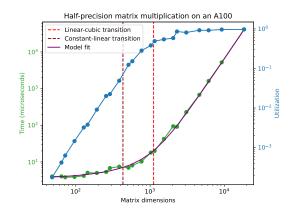

Figure 5: Default cuBLAS GEMM kernel performance on an A100 GPU. The green and blue curves show observed wall clock time and utilization, respectively. The purple curve shows a cubic polynomial fit to wall clock time, with dashed lines at the boundaries between a constant  $\approx 4.5 \ \mu s$ latency-bound regime, a linear (likely occupancy-bound) regime, and a cubic compute-bound regime.

Figure 5 displays empirically observed matrix multiplication latencies on an A100, showing a  $\approx 4.5 \ \mu s$  timescale below which the matrix multiplications cannot be accelerated due to various overheads of off-theshelf cuBLAS kernels. Other GPUs are similar. Network latencies are also on the order of microseconds (Section 4.3) for an optimized all-reduce in which latency does not scale with the number of participants (e.g. a mesh network topology), so even a more optimized matrix multiplication kernel won't change our bottom line too much.<sup>12</sup> To account for both factors, we take  $t_L = 9 \ \mu s$ . Then given a training duration  $t_{\text{train}}$ of 3 months, and typical values of  $b = 4 \times 10^6$ , L = 100, Eq. 14 for a dense model (E = 1) becomes

$$\mathbf{T}_{\text{critical}} = \mathbf{3} \times \mathbf{10}^{\mathbf{30}} \, \text{FLOP.}$$

(15)

We emphasize again that the quadratic sensitivity to uncertainty makes this an approximate estimate (within one or two orders of magnitude).

A discussion of possible methods to reduce  $t_L$  is beyond our scope, but we note that a reduction by one order of magnitude, to 900 ns, would put it at only several times typical DRAM access latencies, despite the need for an all-reduce operation across inter-node interconnects, so this is likely a generous lower bound given anything like present interconnect technology. Given the quadratic role of  $t_L$  in Eq. 14, improved interconnects may therefore permit at most two orders of magnitude of further training compute.

<sup>&</sup>lt;sup>12</sup>This does assume some network latency is incurred on a large fraction of MLP blocks, which is true so long as any tensor or expert parallelism is employed, or any significant degree of pipeline parallelism is employed. A purely data-parallel cluster would fail to fit model weights in DRAM, unless fully-sharded (Rajbhandari et al., 2020), which would re-introduce network latencies at most layers.

## 5.1.2 FROM BANDWIDTH

Alternatively, we can consider utilization-preserving minimums imposed on b' and d' by network and memory bandwidth. Each GPU, for each nanobatch, performs two physical matrix multiplications on the forward pass of shape  $(d', d') \times (d', b') \rightarrow (d', b')$ , one for each layer of the expert and MLP block for which it's responsible. This entails  $d'^2b'$  MAC twice in the forward pass and four times in the backward pass (Section 2), for  $6d'^2b'$  MAC in total arithmetic. Furthermore, it participates in a tensor-parallel all-reduce across  $N_{\text{TP, ff}}$ or  $N_{\text{TP, model}}$  peers of the  $d' \times b'$  activation matrix (or its gradient) after each such multiplication, in both the forward and backward pass, receiving approximately 2d'b' words (Eq. 2) for each of four such all-reduces, or 8d'b' words total. This is balanced when

$$\frac{6d'^2b'\operatorname{MAC}}{C} = \frac{8d'b'}{B_{\operatorname{net}}},$$

where C is the GPU's arithmetic throughput in MAC per second, and  $B_{net}$  its unidirectional network bandwidth in words per second. This is solved by

$$d' = \frac{4C}{3B_{\text{net}}} \cdot \frac{1}{\text{MAC}}.$$

(16)

How large is the critical nanobatch size b'? If the weight submatrices (and their gradients) fit in SRAM, the usual reason to require a large nanobatch, i.e. controlling DRAM bandwidth repeatedly accessing weights and their gradients (Section 4.1.1), does not apply. This can potentially occur when the aggregate SRAM of a single model replica exceeds twice the model size:

weights in SRAM

$$\implies \frac{N_{\text{GPU}}}{N_{\text{DP}}} \cdot S \ge 2N_p,$$

where S is the single-GPU SRAM word capacity. Using the substitution  $N_{\text{GPU}}/N_{\text{DP}} = N_{\text{PP}} \cdot N_{\text{EP}} \cdot N_{\text{TP}}$ , our choices above  $N_{\text{PP}} = L$ ,  $N_{\text{EP}} = E$ , the tensor-parallel bandwidth bottleneck (Eq. 9)  $N_{\text{TP}} = d_{\text{ff}}d_{\text{model}}/d'^2$ , and the parameter count formula (Eq. 1)  $N_{\text{p}} = 2LEd_{\text{model}}d_{\text{ff}}$ , we cancel  $N_{\text{p}}$  from both sides to get:

weights in SRAM

$$\implies \frac{S}{d'^2} \ge 4.$$

In this case, we set an aggressive lower bound of

$$b' = 16$$

, (if weights in SRAM)

as tensor core instructions typically require each input dimension to be at least 8, and we assume at least twice as many tokens per nanobatch to support double-buffered data movement, ensuring that the tensor cores are well fed.

Otherwise, we make use of the fact that a typical weight gradient accumulation step entails  $b'd'^2$  MAC and  $d'^2$  DRAM accesses in both directions: once to read the previously-accumulated gradient, and once to write the new gradient. Canceling  $d'^2$  from both sides, the DRAM bottleneck implies:

$$b' = \frac{C}{B_{\text{DRAM}}} \cdot \frac{1}{\text{MAC}},$$

(if weights in DRAM)

where  $B_{\text{DRAM}}$  is the "unidirectional" DRAM bandwidth (half the total bandwidth) in words per second.

Applying Eq. 13 with these formulas, we now estimate the largest possible utilization-preserving training run for recent NVIDIA systems, considering only bandwidth bottlenecks. We do the analysis with a twist: at the *node* level, treating the whole node as a single "GPU". This allows us to identify the tightest constraints since the inter-node bandwidth bottleneck (InfiniBand except in the case of an H100 SuperPOD) is most severe. The results are in Table 2. In most cases, the  $T_{\text{critical}}$  calculated by this method is two to three orders of magnitude below that given by the latency method, making bandwidth the operative constraint on utilization, and leaving only about two orders of magnitude of headroom above today's largest training runs (Epoch AI, 2024).

The increased inter-node bandwidth in a SuperPOD allows for a factor of  $\approx 20$  increase in tensor parallelism, which in turn allows model replicas to be large enough to fit weights and their gradients in SRAM, bypassing DRAM bandwidth bottlenecks and greatly reducing the nanobatch size. As such, the operative constraint in this case is latency (Eq. 15).

### 5.2 The absolute limit

In the previous subsection, we pursued one approach to answering the first question from Section 4, identifying the limits to scale imposed by latencies and bandwidth, assuming good utilization. Aggregate bandwidth and arithmetic throughput can in principle be scaled arbitrarily far, though perhaps with large decreases in utilization. But latency imposes hard limits to scale regardless of utilization. We consider those limits here.

If  $t_L$  is the latency of one matrix multiplication as in Section 5.1.1, then a model forward and backward pass must take at least  $4Lt_L$  time no matter how many GPUs we have in the training cluster, for the two matrix multiplications required per each of L MLP blocks in each direction. For a batch size b and Chinchillaoptimal dataset size  $D = 20N_p$ , this means the training duration must be at least  $4Lt_L \cdot (D/b) = 80N_pLt_L/b$ . Setting this equal to the training timescale  $t_{\text{train}}$  and solving for  $N_p$ ,

$$N_{\rm p} = \frac{b}{L} \cdot \frac{t_{\rm train}}{80t_L} \tag{17}$$

is the greatest number of parameters that can be trained over duration  $t_{\text{train}}$ .

|               | Arithmetic           | Unidir. bandwidth (words/s) |                      | SRAM         |       |     | $\mathbf{T}_{critical}$ |

|---------------|----------------------|-----------------------------|----------------------|--------------|-------|-----|-------------------------|

| GPU           | (MAC/s)              | Network                     | DRAM                 | (words)      | d'    | b'  | (FLOP)                  |

| DGX-1 (V100)  | $5.00 	imes 10^{14}$ | $2.5 	imes 10^{10}$         | $1.8 \times 10^{12}$ | 151 <b>M</b> | 26.7k | 278 | $1 \times 10^{27}$      |

| DGX A100      | $1.25\times 10^{15}$ | $1.0 	imes 10^{11}$         | $3.1 \times 10^{12}$ | 366M         | 16.7k | 401 | $3 \times 10^{28}$      |

| DGX H100      | $3.96\times10^{15}$  | $2.0 	imes 10^{11}$         | $6.7 	imes 10^{12}$  | 487M         | 26.4k | 591 | $2 \times 10^{28}$      |

| " in SuperPOD | "                    | $9.0 	imes 10^{11}$         | "                    | "            | 5.9k  | 16  | $1 \times 10^{34}$      |

Table 2: FP16 specs of recent NVIDIA systems (NVIDIA, 2019; 2020; 2022), along with their corresponding critical weight matrix shape  $d' \times d'$  as from Eq. 16 and critical nanobatch size b' (depending on whether weights and their gradients might fit in SRAM), and maximum dense (E = 1) three-month training run size  $T_{\text{critical}}$  as from Eq. 13, assuming  $b = 4 \cdot 10^6$ , L = 100 and considering only bandwidth bottlenecks.

Employing once again the Chinchilla equation 12 for the total training compute, and substituting Eq. 17,

$$T_{\text{limit}} = \frac{3 \,\text{MAC}}{320 \cdot E} \left(\frac{b}{L} \cdot \frac{t_{\text{train}}}{t_L}\right)^2 \tag{18}$$

is the total compute for this latency-limited training run. Interestingly, this is exactly nine times as large as Eq. 14, the latency-imposed limit on *utilization-preserving* training runs. This factor of nine is attributable to the replacement of an *efficient* pipeline schedule with a *latency-minimizing* pipeline schedule.

Taking our usual values  $b = 4 \times 10^6$ , L = 100,  $t_{\text{train}} = 3$  months,  $t_L = 9 \ \mu s$  gives

$$\begin{vmatrix} \mathbf{N}_{\text{p}} = \mathbf{4} \times \mathbf{10^{14}}, \\ \mathbf{T}_{\text{limit}} = \mathbf{2} \times \mathbf{10^{31}} \text{ FLOP} \end{vmatrix}$$

as the number of parameters and training compute of the largest dense model that can be trained over  $t_{\text{train}}$  duration, even at low utilization. We emphasize yet again that the quadratic sensitivity to uncertainty makes this an approximate estimate.

As in Section 5.1, this estimate depends on b and L through their ratio. In Appendix 8.3, we consider an optimistic scenario where the batch size can be scaled much faster than the layer count, in which  $T_{\text{limit}}$  could be as high as  $3 \times 10^{36}$  FLOP, which is so large that a training run of that size would exceed annual world primary energy consumption. Whether latencies are of practical relevance or not, therefore, may heavily depend on how aggressively batch sizes can be scaled relative to the layer count of large models.

# 6 COMPLETE MODEL AND RESULTS

### 6.1 MODEL SPECIFICATION

Our model has the following pieces:

- 1. Assumptions about how the critical batch size b, the training dataset size D, and the model dimensions  $d_{\text{model}}, d_{\text{ff}}, E, L$  should scale as models are increased in size.

- A model of matrix multiplications on a single GPU. This model incorporates HBM, L2, and L1

memory bandwidth bottlenecks, and the resulting under-utilization of streaming multiprocessors

on NVIDIA GPUs when the matrix multiplications become unusually small.

- 3. A hierarchical network description. We ignore network topology for the most part but take into account that different levels in a network hierarchy (e.g. intra-node and inter-node) will have different bandwidths and latencies at which they can facilitate communication across GPUs. For instance, such a description could look like "we have an NVLink node size of 8, the NVLink bandwidth is 600 GB/s bidrectional per GPU with  $10 \ \mu \text{s}$  one-way latency, and inter-node communication takes place at 50 GB/s bidirectional per GPU with  $5 \ \mu \text{s}$  one-way latency."